回路設計ソフトウェアとは

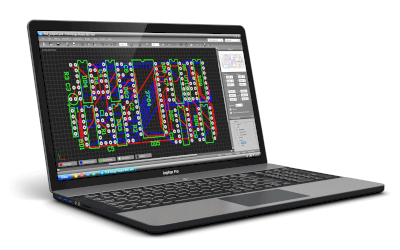

回路設計ソフトウェアとは、集積回路、電子機器、電気回路などの設計作業を支援するソフトウェアです。

回路設計支援用のハードウェアと合わせて、EDA (Electronic Design Automation) とも呼ばれることもあります。従来は手作業で行われていた電子機器の設計を回路設計ソフトウェアを使ってある程度自動的に実施することで、開発のスピードを上げ、ミスのない安全な設計を実現します。

手動設計の時代には回路図を用いた設計が行われていましたが、回路設計ソフトウェアを用いた設計では、機能を設計専用の言語で記述してそれを回路に自動的に変換することで回路設計を行います。

回路設計ソフトウェアの使用用途

回路設計ソフトウェアは、電子・電気回路を設計・開発する分野では必ず使用されています。半導体メーカーでは、集積回路のパーツとなるデバイス設計、集積回路のシステム設計・アーキテクチャ設計、論理設計、回路設計、レイアウト設計および各段階におけるシミュレーションなど設計に関わる全ての段階で、回路設計ソフトウェアが使われます。

また、サーバ、IoT機器、医療機器、産業機器、通信機器などの分野でも、プリント基板の設計、基板上での電子部品配置・配線、機能テストなどで、回路設計ソフトウェアが有用です。

回路設計ソフトウェアの原理

回路設計ソフトウェアを用いた設計では、次のようなフローで回路設計を行います。

1. HDLを用いた設計

まず、必要とされる機能をVerilogなどのハードウェア記述言語 (HDL: Hardware Description Language) で表します。この部分は、通常、回路設計ソフトウェアではなく設計者の手作業で行われます。

HDLより上位のシステムレベルの設計言語から、自動的にHDLに変換してくれるシステムもありますが、その場合は、システムレベルの設計を手作業で行います。

2. 論理回路への変換

HDLによる設計が終わり、その設計が意図した通りの動作をすることをテストベンチで検証した後、回路設計ソフトウェアがHDLを論理合成して論理回路へと変換します。回路設計ソフトウェアは、既存デバイスの情報をライブラリとして持っていて、設計ルールに従ってライブラリの中から適切なデバイスを自動的に選択します。

3. シミュレーション

回路設計ソフトウェアは、論理合成してできた論理回路に対してシミュレーションを行い、HDL設計後のテストベンチ同様、要求される機能を満たしていることを検証します。この段階の検証では、ライブラリが持つデバイスのタイミング情報なども含んだ検証を行うため、信号の値が0か1かという単純な検証ではなく、信号の値が不定 (X) である状態も含めて機能検証が行われます。

4. レイアウト設計

論理回路が機能要求を満たすことを確認した後、決められたサイズのチップ上または基板上に効率よくデバイスを配置し、信号間を配線します。これ以降の段階は、回路設計ではなくレイアウト設計と呼ばれ、一般的には回路設計ソフトウェアに含まれません。

回路設計ソフトウェアのその他情報

ハードウェア記述言語の種類

回路設計に使用するハードウェア記述言語にはVerilogとVHDLの2種類があります。

1. Verilog

C言語やPascalと記法や構文が似ており、記述が他のHDLと比較して簡潔で初学者が学習しやすいと言われています。シミュレーション用の機能が豊富です。1995年にIEEE 1364として標準化されました。

2. VHDL

ALGOLやAdaと記法や構文が似ており、厳密なデータ型を用いるため初学者にとってとっつきにくい言語と言われています。機能が豊富で抽象度の高い記述が可能です。1987年にIEEE 1076として標準化されました。

HDLとソフトウェア用プログラミング言語とは、本質的な違いがあります。ソフトウェア用のプログラミングでは基本的には記載された順でシーケンシャルに処理が進みます。ソフトウェアでは単一のCPUで動作し、複数の処理を同時に並行して動作することを想定していないためです。

一方で、HDLで記述された回路は同時並行的に動作します。ハードウェアを構成する部品は入力信号を受け取ればいつでも動作可能のためです。