What Is a Programmable Delay Line?

A programmable delay line is a type of electronic circuit called a delay line that delays the propagation time of an electrical signal.

The delay time can be changed by programming. In addition, there are passive delay lines consisting only of passive elements and active delay lines that can be driven by external ICs.

By delaying a signal for an arbitrary amount of time, it is possible to match the timing with other signals or to intentionally add a time difference. They are used in a wide variety of electronic devices, including communications equipment.

Uses of Programmable Delay Lines

Programmable delay lines are used to match the timing of data and clock signals. It is especially important to be able to adjust the timing precisely, since the higher the speed, the more likely it is that slight timing deviations will cause problems.

Other applications include signal pulse width conversion, oscillator circuits, frequency multipliers and frequency discriminators. Applications include medical, broadcasting, military, and space. Programmable delay lines are used in various detection and communication devices where precise timing is required.

Principle of Programmable Delay Lines

A programmable delay line is a simple principle that uses inductance L and capacitance C to delay the propagation of electrical signals. It is considered difficult to create a delay line that delivers a specified delay time with high accuracy even when conditions such as process, temperature, and voltage change.

One way to improve accuracy is through feedback. The error against the specified delay time is determined and fed back to the delay line to reduce the error. The delay time is controlled by adjusting the supply voltage, for example. Higher voltage can shorten the delay time.

One way to determine the delay error is to convert the voltage to a frequency. Inverting the output of the delay line and feeding it back to the input produces a frequency output of 1/2 the delay time. This mechanism is called a voltage controlled oscillator (VCO).

Structure of a Programmable Delay Lines

A programmable delay line consists of a delay line that delays a signal and a multiplexer that selects a desired delay time. There are several ways to construct a delay line, and currently the most used is a ladder-type transmission network with inductance L and capacitance C.

The delay time for an N-stage ladder-type circuit is √(L x C) per section, or N x √(L x C) in total. Another configuration is to use a voltage-controlled delay line (VCDL) in which the propagation delay time of the logic gates is controlled by the supply voltage.

The desired delay time can be obtained by selecting an arbitrary stage of the ladder-type circuit with an address signal at the multiplexer. When using programmable delay lines, it is important to consider characteristics such as accurate delay time, good frequency and phase characteristics, low loss, and good temperature characteristics to meet the performance and bit count required for the application.

Other Information on Programmable Delay Lines

1. Characteristic Impedance

Delay lines are transmission lines like coaxial cables and have inherent transmission impedance. The characteristic impedance is a parameter that depends on the inductance and capacitance in the circuit. It is important that the characteristic impedance be uniform within the delay line in order to transmit with minimal waveform distortion.

2. Rise Time

The rise time inherent in a delay line limits the minimum transmission pulse width. Narrower pulse widths have higher frequency components and therefore require faster rise times.

The pulse width that can pass through the delay line without difficulty must be at least three times the rise time inherent in the delay line.

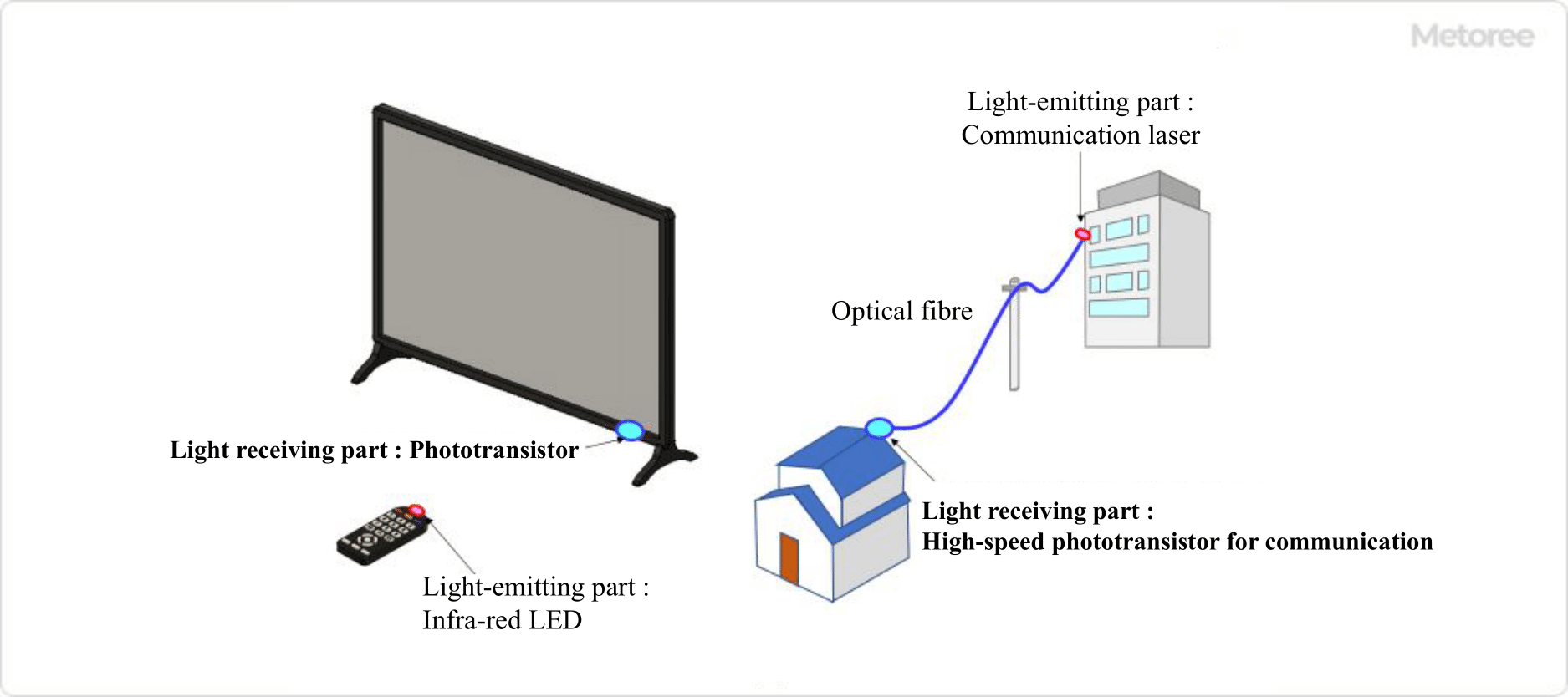

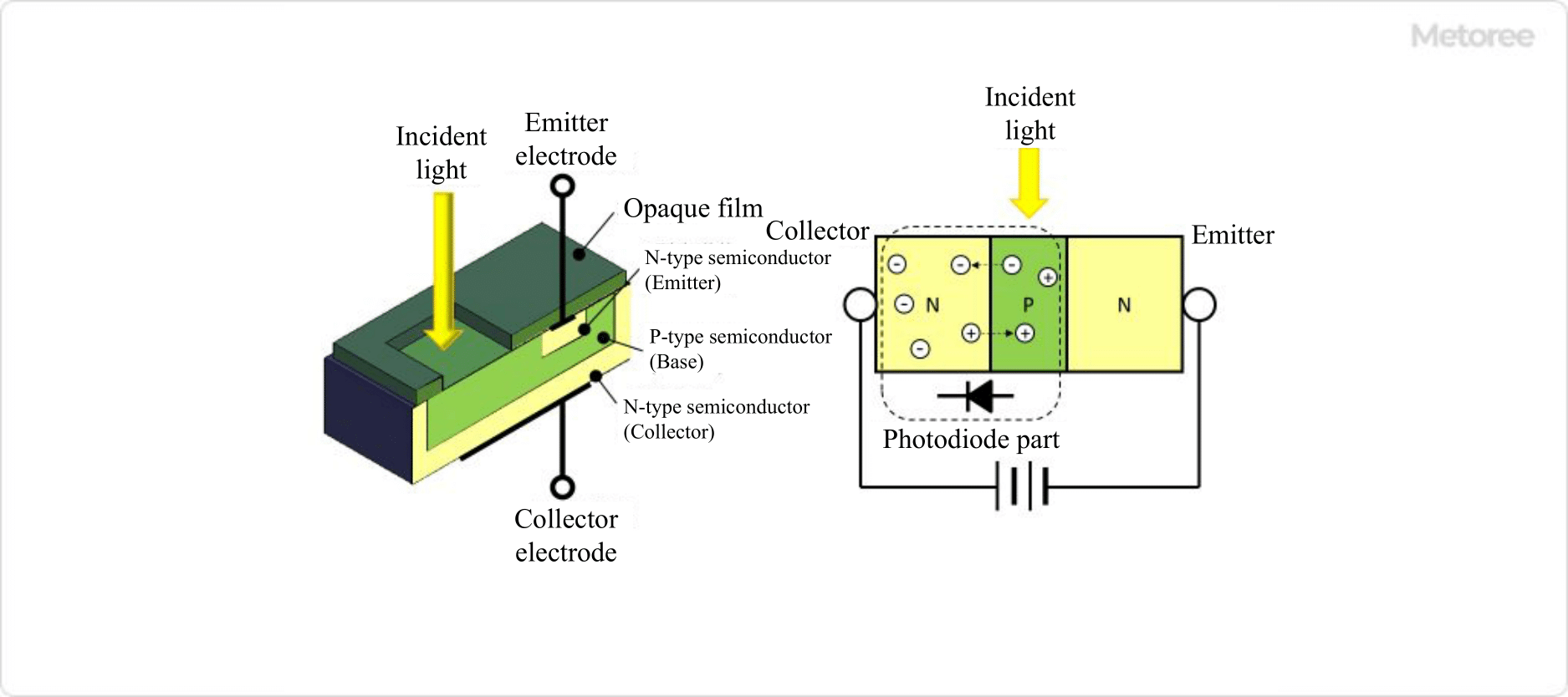

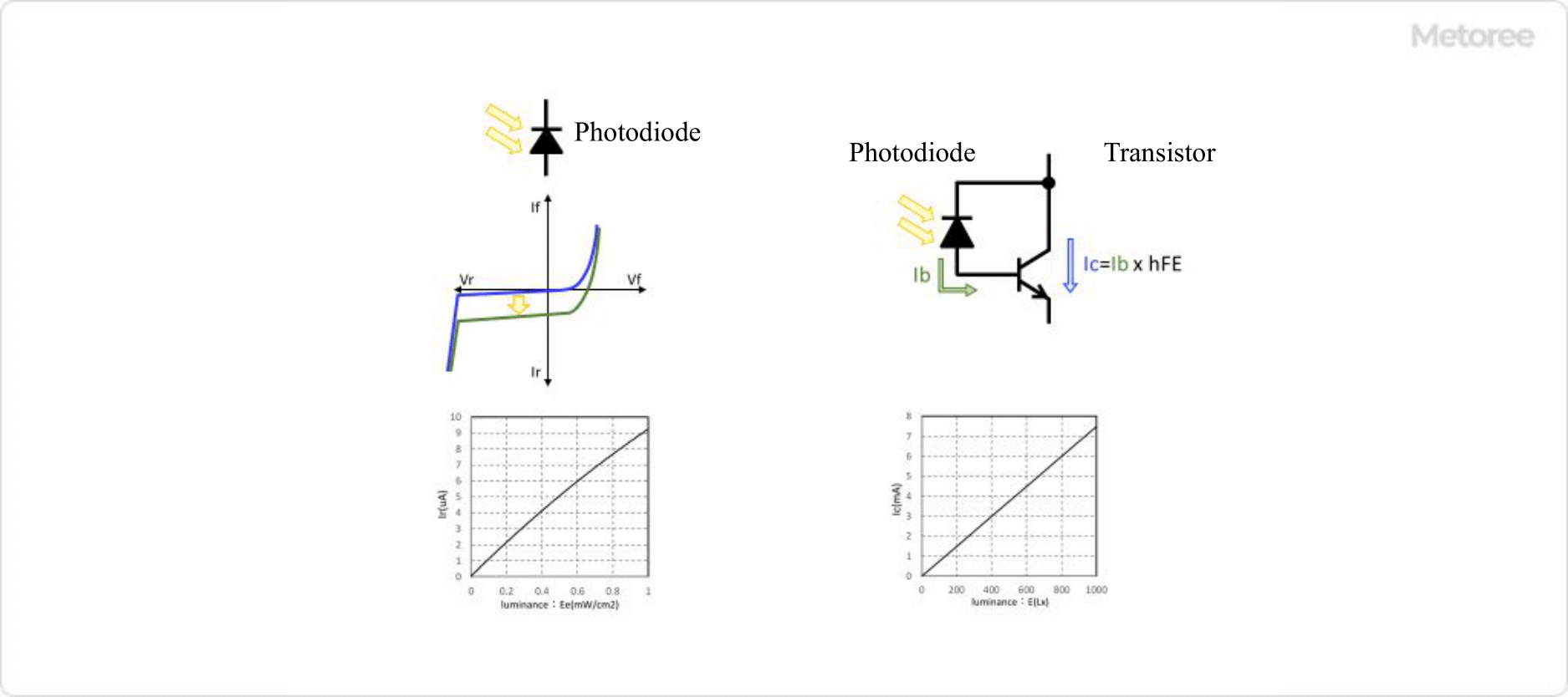

A phototransistor is a semiconductor device used to detect light.

A phototransistor is a semiconductor device used to detect light.

X-ray inspection equipment are devices that can accurately identify elements and hazardous substances in areas invisible to the eye without destroying the object.

X-ray inspection equipment are devices that can accurately identify elements and hazardous substances in areas invisible to the eye without destroying the object.